# **P1022DS** Integrated media and communications processor development system

## Overview

The P1022/P1013 development system (P1022DS) is ideal for hardware and software development for embedded applications. It leverages the highly integrated QorlQ P1022 processor, a Freescale Energy-Efficient product solution, and leading-edge external components.

The high level of integration in the P1022 processor helps to lower system costs, improve performance and simplify board design. The P1022 processor supports:

# Dual e500 Cores Built on Power Architecture® Technology

- 800–1067 MHz

- 256 KB frontside L2 cache with ECC, hardware cache coherent

- 36-bit physical addressing, DP-FPU

System Unit

- 64-/32-bit DDR2/DDR3 with ECC

- Integrated SEC 3.3 security engine

- Open-PIC interrupt controller, performance monitor, 2 x I<sup>2</sup>C, timers, 16 GPIOs, DUART

- 16-bit enhanced local bus supports booting from NAND flash memory

- Up to two USB 2.0 host controller with ULPI interface

- SPI controller supports booting from SPI serial flash memory

- SD/MMC card controller supports booting from flash cards

- Up to two 10/100/1000 Ethernet controllers (eTSEC) with Jumbo Frame support, SGMII interface

- Enhanced features: Parser/filer, QOS, IP-checksum offload, lossless flow control

- IEEE<sup>®</sup> 1588 v2 support

- Three PCI Express® 1.0a controllers

- Two SATA controllers

- I<sup>2</sup>S/TDM interface

- LCD interface

- Packet lossless deep sleep

The P1013 is a single-core version of the P1022. The P1022 processor also integrates an optional hardware encryption block that supports different algorithms for high-performance data that is critical for supporting secure communications. Devices marked with an E include a security engine. The P1022 also includes integrated dual SATA controllers, LCD interface and I<sup>2</sup>S/TDM audio interface, as well as advanced power management capabilities for Energy Star guidelines with less than 300 mW deep sleep power dissipation.

A board support package (BSP) is preinstalled on the P1022DS. This BSP consists of a boot loader (u-boot) and a generic Power Architecture technology system based on the Linux® kernel. The u-boot binary and the Linux kernel reside in the on-board flash memory with a file system pre-installed on the hard disk shipped in the P1022DS development system.

The P1022DS BSP generation takes advantage of the Linux Target Image Builder (LTIB), a suite of tools that leverages existing open source configuration scripts and source code packages, combining them all into a single BSP generation bundle. The source code packages include boot loader and Linux kernel sources as well as many user-space source code packages to build a complete BSP. The LTIB also provides compiler packages, required to build the BSP. Freescale developers use the LTIB to create BSPs for a multitude of Freescale development markets. The LTIB leverages as many BSP elements as possible for the Freescale markets supported, while offering the flexibility necessary to customize components that require platform-specific modifications.

Many third-party applications are available for the P1022DS. They are typically built on top of the BSP delivered by Freescale and can be installed on the hard disk. To see demonstrations or to acquire details of Freescale's third-party applications for this platform, please contact your local Freescale sales office.

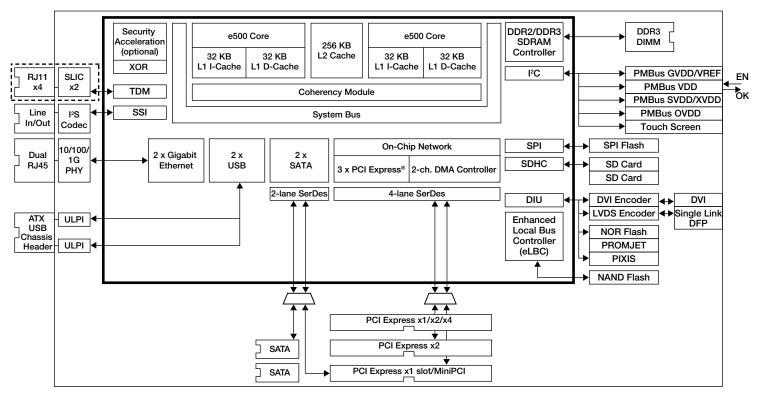

#### P1022DS Block Diagram

### Optional

## P1022 Development System

- P1022 QorIQ communications processor, built on Power Architecture technology

- Memory

- · 64-bit dual-rank DDR3 DIMM with 8-bit ECC support

- 128 MB NOR flash memory

- 1 GB 2K-block NAND flash memory

- 16 MB SPI ROM

- 256B NVRAM

- PCI Express: Three PCI Express interfaces

- SATA: Two independent SATA 2.0 controllers

- Ethernet: Two 10/100/1000Mbps PHYs using RGMII interfaces

- IEEE 1588

- Clock input from precision oscillator

- Dual I<sup>2</sup>C

- · Dual (internal and external) SDHC slot

- · USB: Two USB interfaces

- UARTs: Two DB9 connectors

- SATA2

- TDM: Dual SLIC interfaces

- GPIO: 16

- Two 10/100/1000 Ethernet connectors

- System logic (Pixis FPGA)

- · Manages system reset sequencing

- Manages system bus clock speed selections

- Implements registers for system control and monitoring

- System and DDR clock

- · Can be independently set to one of eight common settings in the interval 66 MHz-166 MHz

- Power supplies

- PMBus controlled supplies for VDD, SVDD/XVDD, OVDD and GVDD

- Video

- Internal LVDS encoder attached 800 x 600 8" LCD panel or DVI

- Audio

- Stereo 24-bit I<sup>2</sup>S audio with headphone output and microphone input

- Documentation

- Reference manual

- Schematics

- Bill of materials

- Board-related documentation

- Configuration guide

- · Software tools

- Linux 2.6.x kernel

- Cross compile and native GNU tool chain

- CodeWarrior USB TAP

Learn More:

For current information about Freescale products and documentation, please visit freescale.com/QorIQ.

Freescale, the Freescale logo and CodeWarrior are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off The Energy-Efficient Solutions logo and QorIQ are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2010, 2011 Freescale Semiconductor, Inc.