The Future of Analog IC Technology

# DESCRIPTION

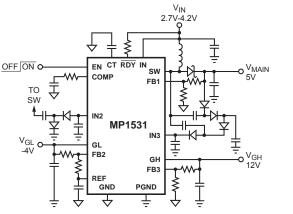

The MP1531 is a triple output step-up converter with charge-pumps to make a complete DC/DC converter to power a TFT LCD panel from a 2.7V to 5.5V supply.

The MP1531 includes a 250kHz fixed frequency step-up converter and a positive and negative linear regulator. The linear regulators are powered via charge-pumps driven by the step-up converter switch node.

A single on/off control enables all 3 outputs. The outputs are internally sequenced at power-on for ease of use. An internal soft-start prevents overloading the input source at startup. Cycle-by-cycle current limit reduces component stress.

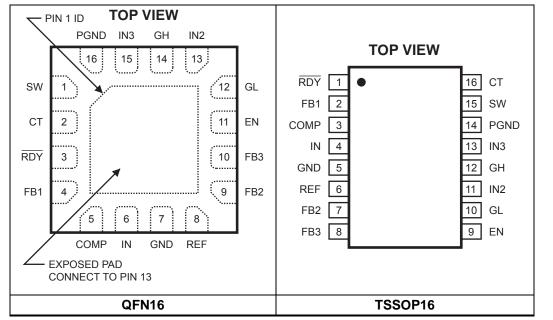

The MP1531 is available in both a tiny 16-pin QFN package (3x3mm) and a 16-pin TSSOP package.

### **EVALUATION BOARD REFERENCE**

| Board Number  | Dimensions            |

|---------------|-----------------------|

| EV1531DQ-002A | 2.3"X x 2.3"Y x 0.5"Z |

## FEATURES

- 2.7V to 5.5V Operating Input Range

- 500mA Switch Current Limit

- 3 Outputs in a Single Package

- Step-Up Converter up to 22V

- Positive 10mA Linear Regulator

- Negative 10mA Linear Regulator

- 250mΩ Internal Power MOSFET Switch

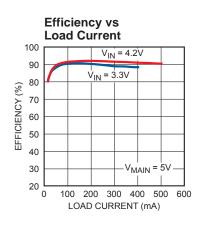

- 95% Efficiency

- 1µA Shutdown Mode

- Fixed 250kHz Frequency

- Positive Regulator up to 38V

- Negative Regulator down to -20V

- Internal Power-On Sequencing

- Adjustable Soft-Start/Fault Timer

- Thermal Shutdown

- Cycle-By-Cycle Over Current Protection

- Under Voltage Lockout

- Ready Flag

- 16-Pin TSSOP and QFN (3x3mm) Packages

### APPLICATIONS

- TFT LCD Displays

- Portable DVD Players

- Tablet PCs

- Car Navigation Displays

For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

### **TYPICAL APPLICATION**

MP1531 Rev. 1.31 5/25/2011

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2011 MPS. All Rights Reserved.

### **ORDERING INFORMATION**

| Part Number | Package       | Top Marking | Free Air Temperature (T <sub>A</sub> ) |

|-------------|---------------|-------------|----------------------------------------|

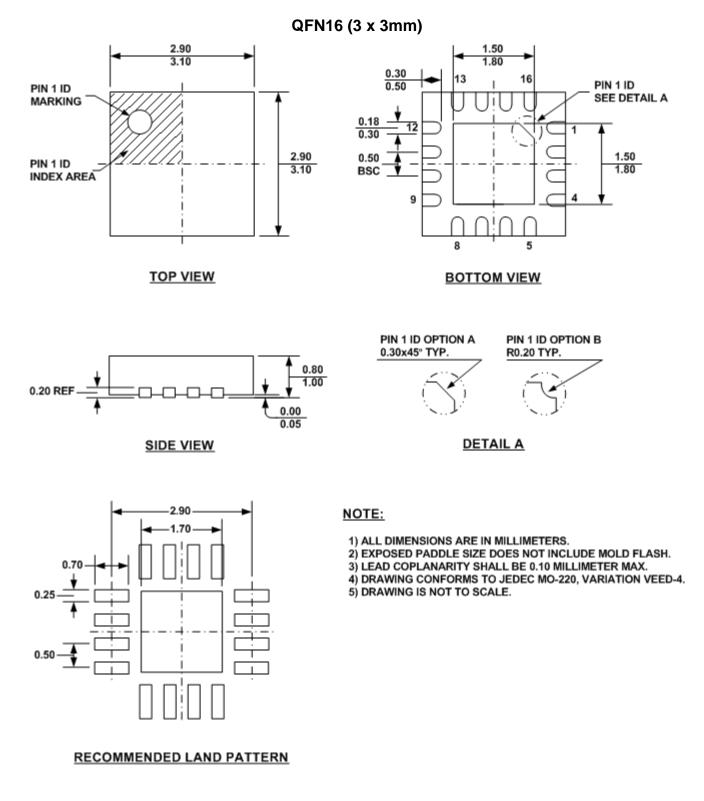

| MP1531DQ*   | QFN16 (3x3mm) | B6          | -40°C to +85°C                         |

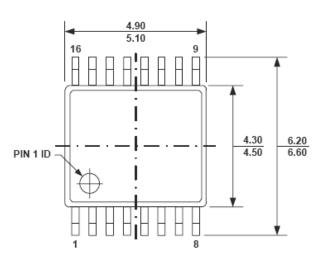

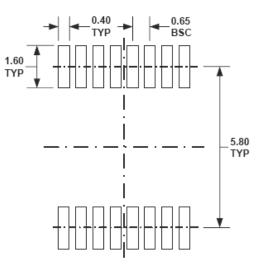

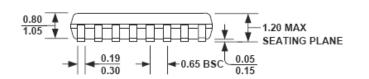

| MP1531DM**  | TSSOP16       | M1531DM     | -40°C to +85°C                         |

\* For Tape & Reel, add suffix -Z (g. MP1531DQ-Z).

For RoHS compliant packaging, add suffix -LF (e.g. MP1531DQ-LF-Z)

\*\*For Tape & Reel, add suffix –Z (g. MP1531DM–Z).

For RoHS compliant packaging, add suffix -LF (e.g. MP1531DM-LF-Z)

### **PACKAGE REFERENCE**

### ABSOLUTE MAXIMUM RATINGS (1)

| IN Supply Voltage              |                                        |

|--------------------------------|----------------------------------------|

| SW Voltage                     |                                        |

| IN2, GL Voltage                |                                        |

| IN3, GH Voltage                |                                        |

| IN2 to IN3 Voltage             | –0.3V to +60V                          |

| All Other Pins                 |                                        |

| Continuous Power Dissipation ( | T <sub>A</sub> = +25°C) <sup>(2)</sup> |

| QFN16 (3 x 3mm)                | 2.1W                                   |

| TSSOP16                        | 1.4W                                   |

| Junction Temperature           | 125°C                                  |

| Lead Temperature               | 260°C                                  |

| Storage Temperature            |                                        |

### Recommended Operating Conditions <sup>(2)</sup>

| Input Voltage       | 2.7V to 5.5V           |

|---------------------|------------------------|

| Main Output Voltage | V <sub>IN</sub> to 22V |

| IN2, GL Voltage     | 0V to –20V             |

IN3, GH Voltage

.0V to 38V

Maximum Junction Temp. (T<sub>J</sub>)

+125°C

Thermal Resistance <sup>(3)</sup>

θ<sub>JA</sub>

θ<sub>JC</sub>

QFN16

.60

120..°C/W

TSSOP16

.90

.30...°C/W

Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_{\rm J}$  (MAX), the junction-to-ambient thermal resistance  $\theta_{\rm JA}$ , and the ambient temperature  $T_{\rm A}$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_{\rm D}$  (MAX) =  $(T_{\rm J}$  (MAX)- $T_{\rm A}$ )/ $\theta_{\rm JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on approximately 1" square of 1 oz copper.

# ELECTRICAL CHARACTERISTICS <sup>(5)</sup>

$V_{IN} = 5.0V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.

| Parameter                          | Symbol               | Condition                                     | Min  | Тур  | Max  | Units |

|------------------------------------|----------------------|-----------------------------------------------|------|------|------|-------|

| Input Voltage Range                | V <sub>IN</sub>      |                                               | 2.7  |      | 5.5  | V     |

| IN Undervoltage Lockout Threshold  | V <sub>UVLO</sub>    | IN Rising                                     | 2.25 |      | 2.65 | V     |

| IN Undervoltage Lockout Hysteresis |                      | ¥                                             |      | 100  |      | mV    |

| IN Shutdown Current                |                      | $V_{EN} \leq 0.3V$                            |      | 0.5  | 1    | μA    |

| IN Quiescent Current               |                      | V <sub>EN</sub> > 2V, V <sub>FB1</sub> = 1.4V |      | 1.2  | 1.6  | mA    |

| EN Input High Voltage              | V <sub>EN-HIGH</sub> | EN Rising                                     | 1.6  |      |      | V     |

| EN Input Low Voltage               |                      |                                               |      |      | 0.3  | V     |

| EN Hysteresis                      |                      |                                               |      | 100  |      | mV    |

| EN Input Bias Current              |                      |                                               |      |      | 1    | μA    |

| Oscillator                         |                      |                                               |      |      |      |       |

| Switching Frequency                | f <sub>SW</sub>      |                                               | 200  | 250  | 300  | kHz   |

| Maximum Duty Cycle                 | D <sub>M</sub>       |                                               | 85   | 90   |      | %     |

| Soft-Start Period                  |                      | C4 = 10nF                                     |      | 6    |      | ms    |

| Turn-Off Delay                     |                      |                                               |      | 3    |      | μs    |

| Error Amplifier                    |                      |                                               |      |      |      |       |

| Error Amplifier Voltage Gain       | Av <sub>EA</sub>     |                                               |      | 400  |      | V/V   |

| Error Amplifier Transconductance   | Gm <sub>EA</sub>     |                                               |      | 1000 |      | μA/V  |

| COMP Maximum Output Current        |                      |                                               |      | ±100 |      | μA    |

| FB1, FB3 Regulation Voltage        |                      |                                               | 1.22 | 1.25 | 1.28 | V     |

| FB2 Regulation Voltage             |                      |                                               | -25  | 0    | +25  | mV    |

| FB1, FB3 Input Bias Current        |                      | $V_{FB1} = V_{FB3} = 1.25V$                   |      | ±100 |      | nA    |

| FB2 Input Bias Current             |                      | $V_{FB2} = 0V$                                |      | ±100 |      | nA    |

| Reference (REF)                    |                      |                                               |      |      |      |       |

| REF Regulation Voltage             |                      | Ι <sub>REF</sub> = 50μΑ                       | 1.22 | 1.25 | 1.28 | V     |

| REF Load Regulation                |                      | 0μA < I <sub>REF</sub> < 200μA                |      | 1    | 1.2  | %     |

| Output Switch (SW)                 |                      |                                               |      |      |      |       |

| SW On Resistance                   |                      | $V_{IN} = 5V$                                 |      | 250  |      | mΩ    |

| SW OII Resistance                  |                      | $V_{IN} = 3V$                                 |      | 400  |      | mΩ    |

| SW Current Limit                   | I <sub>LIM</sub>     |                                               | 0.5  | 0.65 |      | A     |

| SW Leakage Current                 |                      | V <sub>SW</sub> = 22V                         |      | 0.5  | 1    | μA    |

| GL Dropout Voltage (6)             |                      | $V_{GL} = -10V, I_{GL} = 10mA$                |      |      | 0.15 | V     |

| GH Dropout Voltage <sup>(6)</sup>  |                      | V <sub>GH</sub> = 20V, I <sub>GH</sub> = 10mA |      |      | 0.5  | V     |

| GL Leakage Current                 |                      | $V_{IN2}$ = -15V, $V_{GL}$ = GND              |      |      | 1    | μA    |

| GH Leakage Current                 |                      | $V_{IN3}$ = 25V, $V_{GH}$ = GND               |      |      | 1    | μA    |

| Thermal Shutdown                   |                      |                                               |      | 160  |      | °C    |

Notes:

5) Typical values are guaranteed by design, not production tested.

6) Dropout voltage is the input to output differential at which the circuit ceases to regulate against further reduction in input voltage.

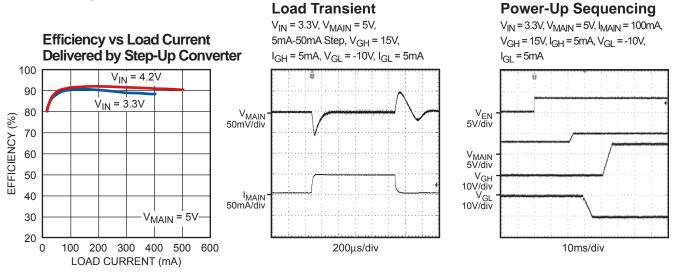

# **TYPICAL PERFORMANCE CHARACTERISTICS**

### Circuit of Figure 3, unless otherwise noted.

| QFN16<br>Pin # | TSSOP16<br>Pin # | Name | Description                                                                                                                                                                                                                                                                                                                              |

|----------------|------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | 15               | SW   | Step-Up Converter Power Switch Node. Connect an inductor between the input source and SW, and connect a rectifier from SW to the main output to complete the step-up converter. SW is the drain of the internal $250m\Omega$ N-Channel MOSFET switch.                                                                                    |

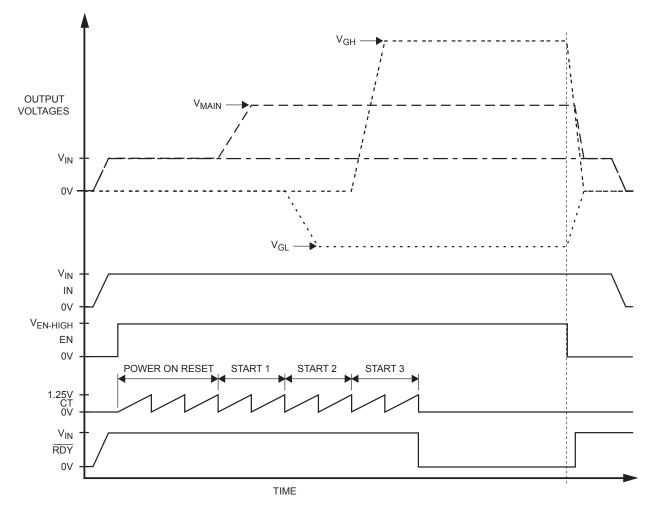

| 2              | 16               | СТ   | Timing Capacitor for Soft-Start and Power-On Sequencing. A capacitor from CT to GND controls the soft-start and sequencing turn-on delay periods. See Power-On Sequencing and Start-Up Timing Diagram.                                                                                                                                   |

|                |                  |      | Regulators Not Ready. This pin is an open drain output, and an external $100 k \Omega$                                                                                                                                                                                                                                                   |

| 3              | 1                | RDY  | pull-up resistor is required for proper operation. During startup RDY will be high impedance. Once the turn-on sequence is complete, this pin will be pulled low if all FB voltages exceed 80% of their specified thresholds. After all regulators are turned-on, a fault in any regulator that causes the respective FB voltage to fall |

|                |                  |      | below 80% of its threshold will cause RDY to go high after approximately $15\mu$ s. If the fault persists for more than approximately 6ms (for C4 = 10nF), the entire chip will shut down. See Fault Sensing and Timer.                                                                                                                  |

| 4              | 2                | FB1  | Step-Up Converter Feedback Input. FB1 is the inverting input of the internal error amplifier. Connect a resistive voltage divider from the output of the step-up converter to FB1 to set the step-up converter output voltage.                                                                                                           |

| 5              | 3                | COMP | Step-Up Converter Compensation Node. COMP is the output of the error amplifier. Connect a series RC network to compensate the regulation control loop of the step-up converter.                                                                                                                                                          |

| 6              | 4                | IN   | Internal Power Input. IN supplies the power to the MP1531. Bypass IN to PGND with a $10\mu$ F or greater capacitor.                                                                                                                                                                                                                      |

| 7              | 5                | GND  | Signal Ground.                                                                                                                                                                                                                                                                                                                           |

| 8              | 6                | REF  | Reference Output. REF is the 1.25V reference voltage output. Bypass REF to GND with a $0.1\mu$ F or greater capacitor. Connect REF to the low-side resistor of the negative linear regulator feedback string.                                                                                                                            |

| 9              | 7                | FB2  | Negative Linear Regulator Feedback Input. Connect the FB2 feedback resistor string between GL and REF to set the negative linear regulator output voltage. FB2 regulation threshold is GND.                                                                                                                                              |

| 10             | 8                | FB3  | Positive Linear Regulator Feedback Input. Connect the FB3 feedback resistor string between GH and GND to set the positive linear regulator output voltage. FB3 regulation threshold is 1.25V.                                                                                                                                            |

| 11             | 9                | EN   | On/Off Control Input. Drive EN high to turn on the MP1531, drive EN low to turn it off. For automatic startup, connect EN to IN. Once the MP1531 is turned on, it sequences the outputs on (See Power-On Sequencing). When turned off, all outputs are immediately disabled.                                                             |

| 12             | 10               | GL   | Negative Linear Regulator Output. GL is the output of the negative linear regulator. GL can supply up to 10mA to the load. Bypass GL to GND with a $1\mu$ F or greater, low-ESR, ceramic capacitor.                                                                                                                                      |

| 13             | 11               | IN2  | Negative Linear Regulator Input. IN2 is the input of the negative linear regulator. Drive IN2 with an inverting charge pump powered from SW. IN2 can go as low as –20V. For QFN package, connect the exposed pad to IN2 pin.                                                                                                             |

| QFN16<br>Pin # | TSSOP16<br>Pin # | Name        | Description                                                                                                                                                                                              |

|----------------|------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14             | 12               | GH          | Positive Linear Regulator Output. GH is the output of the positive linear regulator. GH can supply as much as 10mA to the load. Bypass GH to GND with a $1\mu$ F or greater, low-ESR, ceramic capacitor. |

| 15             | 13               | IN3         | Positive Linear Regulator Input. IN3 is the input to the positive linear regulator. Drive IN3 with a doubling, tripling, or quadrupling charge pump from SW. IN3 voltage can go as high as 38V.          |

| 16             | 14               | PGND        | Power Ground. PGND is the source of the internal $250m\Omega$ N-Channel MOSFET switch. Connect PGND to GND as close to the MP1531 as possible.                                                           |

| Pad            |                  | Exposed pad | No internal electrical connections. Solder it to the lowest potential (IN2 pin) plane to reduce thermal resistance.                                                                                      |

# PIN FUNCTIONS (continued)

### **OPERATION**

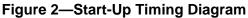

The MP1531 is a step-up converter with two integrated linear regulators to power TFT LCD panels. Typically the linear regulators are powered from diode charge-pumps driven from the switch node (SW). The user can set the

positive charge-pump to be a doubler, tripler, or quadrupler to achieve the required linear regulator input voltage for the selected output voltage. Typically the negative charge-pump is configured as a 1x or 2x inverter.

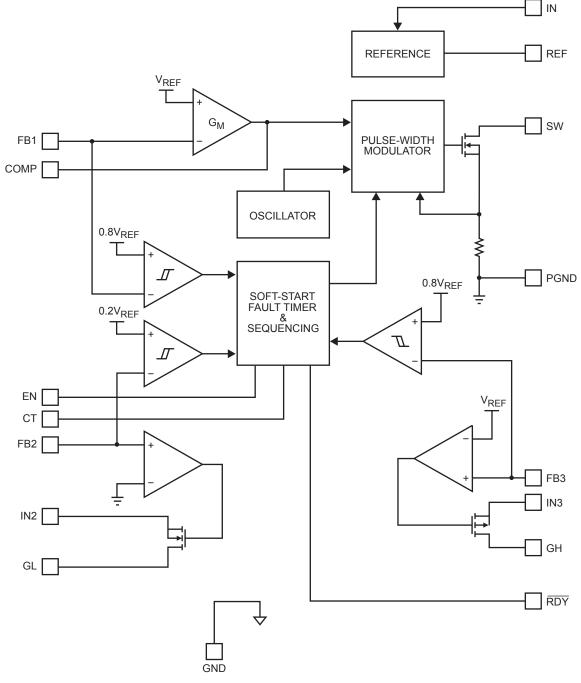

Figure 1—Functional Block Diagram

### Step-Up Converter

The 250kHz fixed-frequency step-up converter employs a current-mode control architecture that maximizes loop bandwidth to provide fasttransient responses needed for TFT LCD drivers. High switching frequency allows for smaller inductors and capacitors minimizing board space and thickness.

### **Linear Regulators**

The positive linear regulator (GH) uses a P-Channel pass element to drop the input voltage down to the regulated output voltage. The feedback of the positive linear regulator is a conventional error amplifier with the regulation threshold at 1.25V.

The negative linear regulator (GL) uses a N-Channel pass element to raise the negative input voltage up to the regulated output voltage. The feedback threshold for the negative linear regulator is ground. The resistor string goes from REF (1.25V) to FB2 and from FB2 to GL to set the negative output voltage,  $V_{GL}$ .

The difference between the voltage at IN3 and the voltage at IN2 is limited to 60V abs. max.

### **Fault Sensing and Timer**

Each of the 3 outputs has an internal comparator that monitors its respective output voltage by measuring the voltage at its respective FB input. When any FB input indicates that the output voltage is below approximately 80% of the correct regulation voltage, the fault timer enables and the RDY pin goes high impedance. The fault timer uses the same CT capacitor as the soft-start sequencer. If any fault persists to the end of the fault timer (One CT cycle is 6ms for a 10nF capacitor), all outputs are disabled. Once the outputs are shut down due to the fault timer, the MP1531 must be re-enabled by either cycling EN or by cycling the input power. When reenabled, the MP1531 cycles through the normal power-on sequence. If the fault persists for less than the fault timer period, RDY will be pulled low and the part will function as though no fault has occurred.

### **Power-On Sequencing and Soft-Start**

The MP1531 automatically sequences its outputs at startup. When EN goes from low to high, or if EN is held high and the input voltage  $V_{IN}$  rises above the under-voltage lockout threshold, the outputs turn on in the following sequence:

- 1. Step-up converter

- 2. Negative linear regulator (GL)

- 3. Positive linear regulator (GH)

Each output turns on with a soft-start voltage ramp. The soft-start ramp period is set by the timing capacitor connected between CT and GND. A 10nF capacitor at CT sets the soft-start ramp period to 6ms. The timing diagram is shown in Figure 2.

After the MP1531 is enabled, the power-on reset spans three periods of the CT ramp. First the step-up converter is powered up with reference to the CT ramp and allowed one period of the CT ramp to settle. Next the negative linear regulator (GL) is soft-started by ramping REF, which coincides with the CT ramp, and also allowed one CT ramp period to settle.

The positive linear regulator (GH) is then soft-started and allowed to settle in one period of CT ramp. Nine periods of the CT ramp have occurred since the chip enabled. If all outputs are in regulation (>80%), the CT will stop ramping and be held at ground. The RDY pin will be pulled down to an active low. If any FB voltage remains below regulation (<80%) after the nine CT periods, RDY will remain high and CT will begin its fault timer pulse.

### **APPLICATION INFORMATION**

### **Setting the Output Voltages**

Set the output voltage on each output by selecting the resistive voltage divider ratio. The voltage divider drops the output voltage to the feedback threshold voltage. Use  $10k\Omega$  to  $50k\Omega$  for the low-side resistor of the voltage divider.

For the step-up converter, determine the high-side resistor R1 by the equation:

$$R1 = \frac{V_{MAIN} - V_{FB1}}{\left(\frac{V_{FB1}}{R2}\right)}$$

Where  $V_{\text{MAIN}}$  is the output voltage of the step-up converter.

For the positive charge-pump, determine the high-side resistor R9 by the equation:

$$R9 = \frac{V_{GH} - V_{FB3}}{\left(\frac{V_{FB3}}{R8}\right)}$$

For the negative charge-pump, determine the high-side resistor R7 by the equation:

$$R7 = \frac{-V_{GL}}{\left(\frac{V_{REF}}{R5}\right)}$$

### Selecting the Inductor

The inductor is required to force the higher output voltage while being driven by the input voltage. A larger value inductor results in less ripple current that results in lower peak inductor current. However, the larger value inductor has a larger physical size, higher series resistance, lower saturation current for a given package size.

Choose an inductor that does not saturate at heavy load transients and start-up conditions. A good rule for determining the inductance is to allow the peak-to-peak ripple current to be approximately 30-50% of the maximum input current. Make sure that the peak inductor current is below the device current limit to prevent loss of regulation. Calculate the required inductance value by the equation:

$$L1 = \frac{V_{IN} (V_{MAIN} - V_{IN})}{V_{MAIN} \times f_{SW} \times \Delta I}$$

Where  $V_{IN}$  is the input voltage,  $f_{SW}$  is the switching frequency, and  $\Delta I$  is the peak-to-peak inductor ripple current.

#### Selecting the Input Capacitor

An input capacitor is required to supply the AC ripple current to the inductor, while limiting noise at the input source. A low ESR capacitor is required to keep the noise at the IC to a minimum. Since it absorbs the input switching current it requires an adequate ripple current rating. Use a capacitor with RMS current rating greater than the inductor ripple current (see selecting the Inductor to determine the inductor ripple current). The input capacitor in Figure 3 is necessary in most lab setups, but can be reduced in typical application circuits if the source impedance is lower.

Figure 3—Triple Output Boost Application Circuit

To insure stable operation place the input capacitor as close to the IC as possible. Alternately a smaller high quality  $0.1\mu$ F ceramic capacitor may be placed closer to the IC if the larger capacitor is placed further away.

### **Selecting the Rectifier Diodes**

Schottky diodes are recommended for most applications because of their fast recovery time and low forward voltage. Use Schottky diodes with a current rating equal to or greater than 4 times the average output current, and a voltage rating at least 1.5 times  $V_{GH}$  for the positive charge-pump and  $V_{GL}$  for the negative charge-pump. 100mA Schottky diodes such as Central Semiconductor CMPSH-3 are recommended for low current charge-pump circuits.

### Selecting the Output Capacitor of the Step-Up Converter

The output capacitor is required to maintain the DC output voltage. Low ESR capacitors are preferred to keep the output voltage ripple to a minimum. The characteristics of the output capacitor also affect the stability of the regulation control system. A  $10-22\mu$ F ceramic capacitor works well in most applications. In the case of ceramic capacitors, the impedance of the capacitor at the switching frequency is dominated by the capacitance, and so the output voltage ripple is mostly independent of the ESR. The output voltage ripple is estimated to be:

$$V_{\text{RIPPLE}} \cong \frac{(V_{\text{MAIN}} - V_{\text{IN}}) \times I_{\text{LOAD}}}{V_{\text{MAIN}} \times C2 \times f_{\text{SW}}}$$

Where  $V_{RIPPLE}$  is the output ripple voltage,  $I_{LOAD}$  is the load current, and C2 is the capacitance of the output capacitor of the step-up converter.

# Selecting the Number of Charge-Pump Stages

For highest efficiency, always choose the lowest number of charge-pump stages that meets the output requirement.

The number of positive charge-pump stages  $N_{\text{POS}}$  is approximately given by:

$$N_{\text{POS}} \cong \frac{\left(V_{\text{GH}} + V_{\text{DROPOUT}} - V_{\text{MAIN}}\right)}{V_{\text{MAIN}} - 2 \times V_{\text{D}}}$$

Where  $V_D$  is the forward voltage drop of the charge-pump diode, and  $V_{DROPOUT}$  is the

dropout margin for the linear regulator. The positive charge-pump can also be configured based on  $V_{IN}$  for better efficiency. Then the equation will be:

$$N_{POS} \cong \frac{\left(V_{GH} + V_{DROPOUT} - V_{IN}\right)}{V_{MAIN} - 2 \times V_{D}}$$

The number of negative charge-pump stages  $N_{\text{NEG}}$  is approximately given by:

$$\mathsf{N}_{\mathsf{NEG}} \cong \frac{-\mathsf{V}_{\mathsf{GL}} + \mathsf{V}_{\mathsf{DROPOUT}}}{\mathsf{V}_{\mathsf{MAIN}} - 2 \times \mathsf{V}_{\mathsf{D}}}$$

Use  $V_{DROPOUT} = 0.5V$  for positive charge-pump and  $V_{DROPOUT} = 0.15V$  for negative charge-pump.

### Selecting the Flying Capacitor in Charge-Pump Stages

Increasing the flying capacitor  $C_X$  values increases the output current capability. A 0.33µF ceramic capacitor works well in most low current applications. The flying capacitor's voltage rating must exceed the following:

$$V_{CX} > N \times V_{MAIN}$$

Where N is the stage number in which the flying capacitor appears.

### Step-Up Converter Compensation

The MP1531 uses current-mode control which unlike voltage mode has only a single pole roll off due to the output filter. The DC gain ( $Av_{DC}$ ) is equated from the product of current control to output gain ( $Av_{CSCONTROL}$ ), error amplifier gain ( $Av_{EA}$ ), and the feedback divider.

$$Av_{DC} = A_{CSCONTROL} \times Av_{EA} \times A_{FB1}$$

$$A_{CSCONTROL} = 4 \times \frac{V_{IN}}{I_{LOAD}}$$

$$A_{FB1} = \frac{V_{FB1}}{V_{MAIN}}$$

$$Av_{DC} = \frac{1600 \times V_{IN} \times V_{FB1}}{I_{LOAD} \times V_{MAIN}}$$

The output filter pole is given in hertz by:

$$f_{FILTERPOLE} = \frac{I_{LOAD}}{\pi \times V_{MAIN} \times C2}$$

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2011 MPS. All Rights Reserved. The output filter zero is given in hertz by:

$$f_{FILTERZERO} = \frac{1}{2 \times \pi \times R_{ESR} \times C2}$$

Where  $R_{ESR}$  is the equivalent series resistance of the output capacitor.

With all boost regulators the right half plane zero (RHPZ) is given in hertz by:

$$f_{RHPZ} = \left(\frac{V_{IN}}{V_{MAIN}}\right)^2 \times \frac{V_{MAIN}}{2 \times \pi \times I_{LOAD} \times L1}$$

### **Error Amplifier Compensation**

To stabilize the feedback loop dynamics the error amplifier compensation is as follows:

$$f_{POLE1} \approx \frac{1}{2 \times \pi \times 10^{6} \times C3}$$

$$f_{ZERO1} = \frac{1}{2\pi \times R3 \times C3}$$

Where R3 and C3 are part of the compensation network in Figure 3. A good start is  $5.6k\Omega$  and 10nF. This combination gives about 70° of phase margin and bandwidth of about 35kHz for most load conditions. Increasing R3 and/or reducing C3 increases the loop bandwidth and improves the load transient.

#### **Linear Regulator Compensation**

The positive or negative regulated voltages of two linear regulators are controlled by a transconductance amplifier and a P-channel or N-Channel pass transistor respectively. The DC gain of either LDO is approximately 100dB with a slight dependency on load current. The output capacitor ( $C_{LDO}$ ) and resistance load ( $R_{LOAD}$ ) make-up the dominant pole.

$$f_{LDOPOLE1} = \frac{1}{2 \times \pi \times R_{LOAD} \times C_{LDO}}$$

The pass transistor's internal pole is about 10Hz to 30Hz. To compensate for the two pole system and add more phase and gain margin, a lead-lag resistor capacitor network is necessary.

For the positive linear regulator:

$$f_{\text{POSPOLE1}} = \frac{1}{2 \times \pi \times (\text{R10} + \text{R9} || \text{R8}) \times \text{C7}}$$

$$f_{\text{POSZER01}} = \frac{1}{2 \times \pi \times (\text{R10} + \text{R9}) \times \text{C7}}$$

For the negative linear regulator:

$$f_{\text{NEGPOLE1}} = \frac{1}{2 \times \pi \times (\text{R6} + \text{R7} || \text{R5}) \times \text{C9}}$$

$$f_{\text{NEGZER01}} = \frac{1}{2 \times \pi \times (\text{R6} + \text{R7}) \times \text{C9}}$$

$f_{\text{POSPOLE1}}$  and  $f_{\text{NEGPOLE1}}$  are necessary to cancel out the zero created by the equivalent series resistance ( $R_{\text{LDOESR}}$ ) of the output capacitor.

$$f_{LDOZERO} = \frac{1}{2 \times \pi \times R_{LDOESR} \times C_{LDO}}$$

For component values shown in Figure 3 a  $10\Omega$  and 56pF RC network gives about 45° of phase margin and a bandwidth of about 35kHz on both regulators.

### Layout Considerations

Careful PC board layout is important to minimize ground bounce and noise. First, place the main boost converter inductor, output diode and output capacitor as close to the SW and PGND pins as possible with wide traces. Then place ceramic bypass capacitors near IN, IN2 and IN3 pins to the PGND pin. Keep the charge-pump circuitry close to the IC with wide traces. Locate all FB resistive dividers as close to their respective FB pins as possible. Separate GND and PGND areas and connect them at one point as close to the IC as possible. Avoid having sensitive traces near the SW node and high current lines. Refer to the MP1531 demo board for an example of proper board layout.

# **PACKAGE INFORMATION**

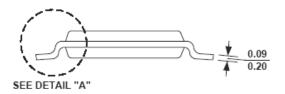

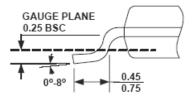

TSSOP16

#### RECOMMENDED LAND PATTERN

FRONT VIEW

TOP VIEW

#### SIDE VIEW

DETAIL "A"

#### NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH,

- PROTRUSION OR GATE BURR.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX.

- 5) DRAWING CONFORMS TO JEDEC MO-153, VARIATION AB.

- 6) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.