메시지

DAC는 시장 전체에서 AI 및 ML의 역할을 탐구합니다.

캘리포니아 샌프란시스코 모스 콘 센터 (Moscone Center), 6 월 25-28 일 DAC 개최

OneSpin 솔루션 과 Austemper Design Systems 기능 안전성 검증을위한 도구를 강조 할 예정입니다. Austemper는 KaleidoScope 도구 모음을 사용하여 미션 크리티컬 한 시스템 개발에 중점을두고 동시 혼합 신호 오류 전파를위한 아날로그 설계를 지원합니다. 자동화 툴 세트는 인증 지향 애플리케이션을위한 안전 분석, 합성 및 검증 기능을 갖추고 있습니다. ADAS 및 자율 주행의 대규모 자동차 설계에 사용됩니다. 동시 오류 시뮬레이션에는 ASIL 요구 사항을 준수하기 위해 ISO 26262에서 권장하는 시뮬레이션이 포함됩니다.

이 회사는 최근 OneSpin Solutions와 파트너 관계를 맺고 OneSpin 부스에서 시연 될 설계 및 검증 흐름을 결합하여 기능 안전 애플리케이션을위한 도구 지원 방법론을 채택했습니다. 하드웨어 안전 메커니즘이 칩 설계에 삽입되고 OneSpin Solutions의 도구는 하드웨어 안전 로직을 공식적으로 검증합니다. 동등성 검사는 삽입 된 안전 로직이 일반 기능에 영향을 미치지 않도록하며 결함 검출 분석은 무작위 오류 발생시 안전 메커니즘이 올바르게 수행되는지 확인합니다.

OneSpin은 TÜV SÜD의 도구 개발 프로세스에 대한 검증을 거쳐 Tool Qualification Kit를 홍보하고 있습니다. 초기 키트는 회사의 360 EC-FPGA EDA 툴에서 사용할 수 있으며, FPGA 순차적 등가성 검사를 통해 FPGA 설계 흐름에서 구현 오류가 발생하지 않도록한다. 이 키트는 ISO 26262, IEC 61508 및 EN 50128 인증을 받았습니다.

FPGA 통찰력

FPGA 디자인을 사용하면, Plunify 자일링스와 협력하여 클라우드에서 Plunify Cloud 플랫폼을 통해 Vivado 디자인 스위트를 제공한다. 설계자는 라이센스를 포함하여 Amazon Web Services (AWS) 클라우드에서 Vivado 프로젝트를 컴파일하기 위해 50c를 지불합니다.

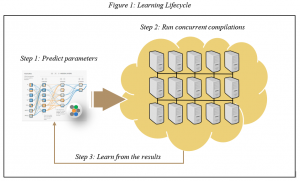

이 회사는 클라우드에서 FPGA 타이밍을 최적화하기 위해 InTime 타이밍 클로저 소프트웨어의 향상된 기능을 시연 할 것이다 (그림 1). InTime Optimization Methodology는 클럭 주파수를 20 ~ 80 % 향상시킬 수 있으며 기계 학습을 통해 몇 주일이 아닌 며칠 만에 타이밍 요구 사항을 충족 할 수 있습니다. 이 소프트웨어는 또한 타이밍 클로저와 최적화를 가속화하며 클라우드를 통해 액세스됩니다.

이 회사는 클라우드에서 FPGA 타이밍을 최적화하기 위해 InTime 타이밍 클로저 소프트웨어의 향상된 기능을 시연 할 것이다 (그림 1). InTime Optimization Methodology는 클럭 주파수를 20 ~ 80 % 향상시킬 수 있으며 기계 학습을 통해 몇 주일이 아닌 며칠 만에 타이밍 요구 사항을 충족 할 수 있습니다. 이 소프트웨어는 또한 타이밍 클로저와 최적화를 가속화하며 클라우드를 통해 액세스됩니다.

eFPGA 기술 홍보, Achronix 반도체 IP 전문가와 협력 중이다. 캐스트 처리량을 높이고 메모리 저장 공간을 절약 할 수 있습니다.

두 업체는 CAST의 무손실 압축 IP가 데이터 센터 및 모바일 에지 데이터 전송 애플리케이션에 사용하기 위해 Achronix FPGA 포트폴리오에 어떻게 포팅되었는지 설명 할 예정이다. Deflate, GZIP 및 ZLIB에 대한 무손실 압축 표준의 하드웨어 구현은 압축 또는 압축 해제에 사용되는 소프트웨어 구현과 호환되며 낮은 압축 및 낮은 대기 시간으로 최대 100Gbit / s 처리량을 제공하고 Speedcore eFPGA 기술과 결합하여 큰 이동 및 저장 저전력 소모의 데이터.

CAST는 IP를 Achronix의 FPGA에 이식했습니다.

에너지 효율

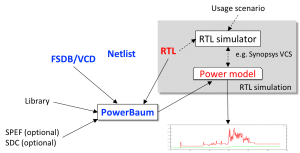

전원 관리에 대해 말하면서, 다른 출품자, 바움는 에너지 효율성을 칩 설계에서 가장 저개발 영역으로 인식합니다. 자동 전력 분석 및 모델링 도구는 자동차, IoT, 모바일, 네트워킹 및 서버 프로젝트 용으로 설계되었습니다. PowerBaum 2.0 (그림 3)은 동적 및 정적 전력을 지원하고 RTL 및 넷리스트 설명을 사용하며 하드웨어 에뮬레이션을 사용하여 전력 분석을 지원합니다. 이 회사는 엔지니어가 현실적인 소프트웨어 시나리오에서 전력 버그를 수정할 수 있다고 설명합니다. 이 툴은 설계자가 지정한 임의의 온도에서의 분석을 지원하여 설계의 전력 소비에 대한 온도의 영향을 평가합니다.

DAC는 전력 모델링을 위해 PowerBaum과 통합 될 게이트 레벨 전력 분석 엔진 인 PowerWurzel도 소개 할 예정이다.

그림 3 Baum의 도구는 에너지 효율성을 분석합니다.

IC 설계를위한 클라우드 기반 SoC 설계 및 검증 툴 측정 항목 시뮬레이션 요구 사항 및 리소스를 관리하고 매분마다 위 또는 아래로 조정하는 클라우드 시뮬레이터 및 검증 관리자를 포함하십시오. 이 회사는 Google Cloud가 UVM 준수 SystemVerilog 시뮬레이션 기능 및 네이티브 웹 기반 검증 관리를 무제한 제공하여 회귀 시간 단축, 트렁크 코드 오류 감소 및 예측 가능한 코드 적용을 가능하게한다고 주장합니다.

이 행사는 참가 업체를 제외하고 기술 세션과 주제별 영역을 다루는 기조 연설 프로그램을 개최합니다. 올해 예를 들어, Cadence는 '자동차 애플리케이션의 기능적 안전성 및 신뢰성'에 대한 자습서와 기계 학습 ( '기계 학습은 다음 단계로 음성 인식 성능 획득')에 관한 자습서를 진행합니다. 6 월 25 일 월요일 Instrumental의 Anna-Katrina Shedletsky 기조 연설은 '자동화 학습 : 기계 학습과 제조의 미래'에 중점을 둘 것입니다. ML 및 AI를 사회적 보조 로봇 (SAR)에 사용하는 것은 남부 캘리포니아 대학의 Maja Matarić 목요일 기조 연설에서 'Automation vs Augmentation : Socially Assistive Robotocs 및 Work of Work'를 발표 할 예정이다.

또 다른 기조 연설은 RISC-V가 독점적 인 명령 집합 아키텍처 (ISAs)에서 설계자를 해방시키는 수단이라고 주장합니다. David A Patterson, Google 및 University of California는 '컴퓨터 아키텍처를위한 새로운 골든 에이지 : 도메인 별 액셀러레이터 및 개방형 RISC-V'를 발표 할 예정입니다.

올해 DAC의 새로운 영역은 Design Infrastructure Alley입니다. 의 주도권 ESD 동맹 협회 고성능 컴퓨팅 전문가를위한 전자 시스템 및 구성 요소의 설계를위한 IT 인프라 전용 영역입니다. 클라우드의 설계 및 관리 사용을위한 컴퓨팅 및 스토리지 요구 사항뿐만 아니라 라이센스 관리, 그리드 컴퓨팅 및 데이터 보안을 논의하는 전용 Design-on-the-Cloud 파빌리온 극장이 있습니다.